HAL v4.2 releases: The Hardware Analyzer

HAL- Hardware Analyzer

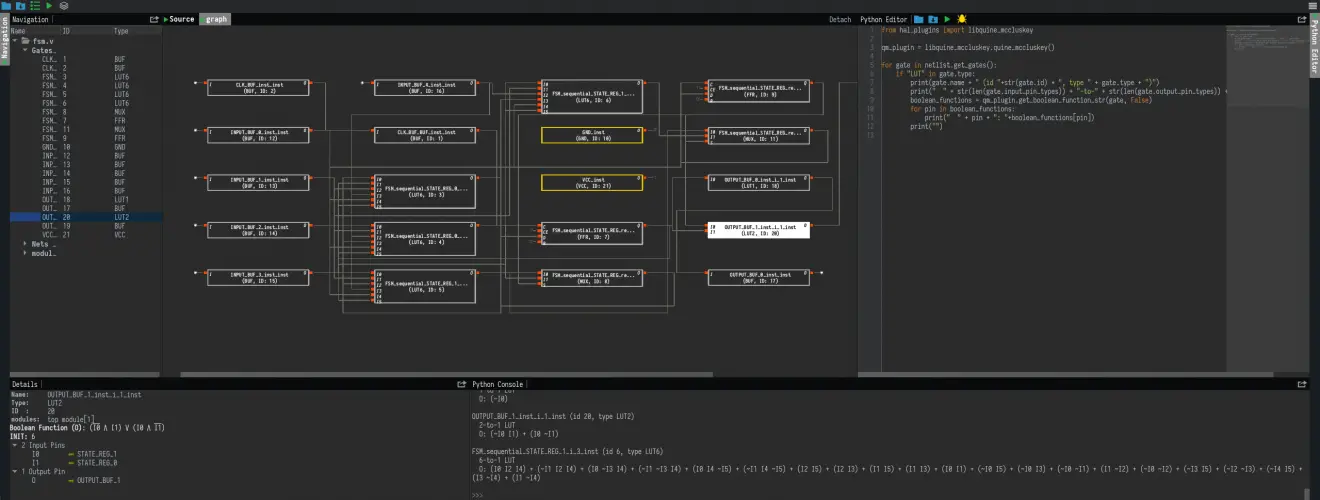

Hardware Analyzer (HAL) [/hel/] is a comprehensive reverse engineering and manipulation framework for gate-level netlists focusing on efficiency, extendability, and portability. HAL comes with a fully-fledged plugin system, allowing it to introduce of arbitrary functionalities to the core.

Features

- Natural directed graph representation of netlist elements and their connections

- Support for custom gate libraries

- High-performance thanks to optimized C++ core

- Modularity: write your own C++ Plugins for efficient netlist analysis and manipulation (e.g. via graph algorithms)

- A feature-rich GUI allowing for visual netlist inspection and interactive analysis

- An integrated Python shell to exploratively interact with netlist elements and to interface plugins from the GUI

Changelog v4.2

- GUI plugin manager

- WARNING: modified plugin core API – reduced number of base classes and instead added extension components

- added overview of loaded plugins and their features

- added interactive buttons to load and unload plugins

- added feature to load plugin automatically if needed for file parsing

- prevent unloading of plugin if it is needed as a dependency of another plugin

- changed plugin load policy to have only mandatory or user required plugins loaded at startup

- Boolean functions

- added

BooleanFunction::substitute(const std::map<std::string, std::string>&)to substitute multiple variable names at once - changed

BooleanFunction::get_constant_valueto returnstd::vector<BooleanFunction::Value>, thereby removing the 64-bit limit - added

BooleanFunction::Node::get_constant_value,BooleanFunction::Node::get_index_value, andBooleanFunction::Node::get_variable_name - added

BooleanFunction::get_constant_value_u64andBooleanFunction::Node::get_constant_value_u64to retrieve the constant value asu64if it comprises less than 64-bit - added

BooleanFunction::has_constant_value(const std::vector<BooleanFunction::Value>&)andBooleanFunction::Node::has_constant_value(const std::vector<BooleanFunction::Value>&) - added

BooleanFunction::algebraic_printeras an alternative printer forBooleanFunction::to_stringto print a Boolean function in algebraic form - added shift and rotate operators

Shl,Lshr,Ashr,Rol, andRor

- added

- plugins

boolean_influence- added deterministic variants of all Boolean influence functions that shall be used for Boolean functions with only few input variables

- added additional parameters for more control to the subcircuit and gate variants of

get_boolean_influence

netlist_preprocessing- added

decompose_gates_of_typeanddecompose_gatethat decompose combinational logic gates into basic gate types - added

parse_def_fileto parse a Design Exchange Format file that contains placement information simplify_lut_initsnow annotates the original init string into the data container

- added

verilog_parser- added annotation of all net names that where merged during parsing in the data container

- added implicit wire declarations for assign statements

- changed the behavior of the parser when flattening a netlist and generating new unique names (instead of appending an index we now add a prefix containing the names of parent modules)

z3_utils- added

compare_netlistsfunction that functionally compares two netlists that only differ in their combinational logic - removed class

z3Wrapper - renamed

to_z3tofrom_bfand added support for missing node types - renamed

to_haltoto_bfand added support for missing node types - changed

to_cppto output only the C++ code implementing the Boolean function and nothing more

- added

dataflow_analysis- added API to interact with dataflow analysis results from C++ and Python

- added automatic creation of pin groups for data and control pins of register modules

- added parameter to only write or retrieve information on certain register groups

- deprecated

plugin_dataflow::executeas its functionality is now split betweendataflow::analyzeand the members ofdataflow::Result - removed file writes if not explicitly called by user

netlist_simulation_controller- added versions of

add_waveform_grouptaking a module pin group as input - added versions of

set_inputtaking aWaveDataobject, vectors of nets and values, aWaveDataGroupand a vector of values, and a module pin group and a vector of values as input

- added versions of

solve_fsm- changed both versions of fsm_solving to now not only consider data inputs of the state register, but also synchronous control signals.

xilinx_toolbox- added the first version of the xilinx_toolbox plugin that provides functionality especially fitted to xilinx fpga netlists

- decorators

- added

NetlistModificationDecorator- added

delete_modulesto delete all (or a filtered subset of) the modules in a netlist - moved

replace_gatefromnetlist_utils, now returns pointer to replacement gate - added

connect_gatesto connect two gates at the specified pins via a new or already existing net - added

connect_netsto merge two nets into one, thereby connecting them

- added

BooleanFunctionDecorator- added a version of

get_boolean_function_fromthat takes a module pin group as input

- added a version of

- added

- selection details widget

- added

Focus item in graph viewto several context menus - added

Isolate in new viewto gate/module related context menus - changed

Isolate in new viewpolicy for modules: open exclusive module view if such a view already exists - improved drag&drop functionality to move module pins and merge module pin groups

- added

- miscellaneous

- added

Gate::get_modulesto recursively get all modules that contain the gate by traversing the module hierarchy - added

Net::is_a_source(const Gate*)andNet::is_a_destination(const Gate*)that check whether a gate is a source/destination independent of the gate pin - added

PinGroup<T>::contains_pinto check whether a pin is part of the respective gate or module pin group - added overloaded version of

deserialize_netlistthat takes a gate library, thereby overruling the gate library path in the .hal file - added

utils::wrapped_stoullandutils::wrapped_stoulthat wrap the standard string to integer conversion and usehal::Result<>for error handlung instead of exceptions - added utility function

is_valid_enumto check whether the string representation of an enum value is valid. - added serialization of physical gate positions (non-negative integer)

- added keyboard shortcuts for fold, unfold, and remove from view

- added

filterparameter toget_fan_[in/out]_[nets/endpoints] - added pyBinds for the

LogManagerclass - added pyBinds for the

ProjectDirectoryclass - added

Module::move_pin_groupto change the order of pin groups of a module - changed abort being more responsive when aborting layouting of large views

- changed and improved color scheme for light style

- changed labels on HAL startup screen to better resemble the new project structure

- removed toolbox from groupings widget

- added

- bugfixes

- fixed build from tarball

- fixed minor navigation bugs on settings page

- fixed missing Python bindings for

GatePinGroup - fixed

SolveFsmPluginnot properly replacing power and ground nets in Boolean functions - fixed searchbar attempting time consuming search when there is no content to search

- fixed some documentations of core functions

- fixed igraph not building anymore by relaxing irgaph compiler options

- fixed Python GUI API being unavailable at runtime

- fixed nets without source or destination not being shown when unfolding the module they belong to in the selection details widget

- fixed cmake failing to parse HAL version number from file

- fixed pins and pin groups not being hashable in Python

- fixed Python script execution abort button disappearing when switching tabs

- fixed segfault when deleting a module for which an exclusive view exists

- fixed not loading all plugins if the GUI is not in control

- fixed Verilog writer not being a dependency of Verilator plugin

Install && Tutorial

Copyright (c) 2019 Ruhr-Universität Bochum, Lehrstuhl für Eingebettete Sicherheit. All Rights Reserved.

Copyright (c) 2019 Marc Fyrbiak, Sebastian Wallat, Max Hoffmann (“ORIGINAL AUTHORS”). All rights reserved.